तपशील

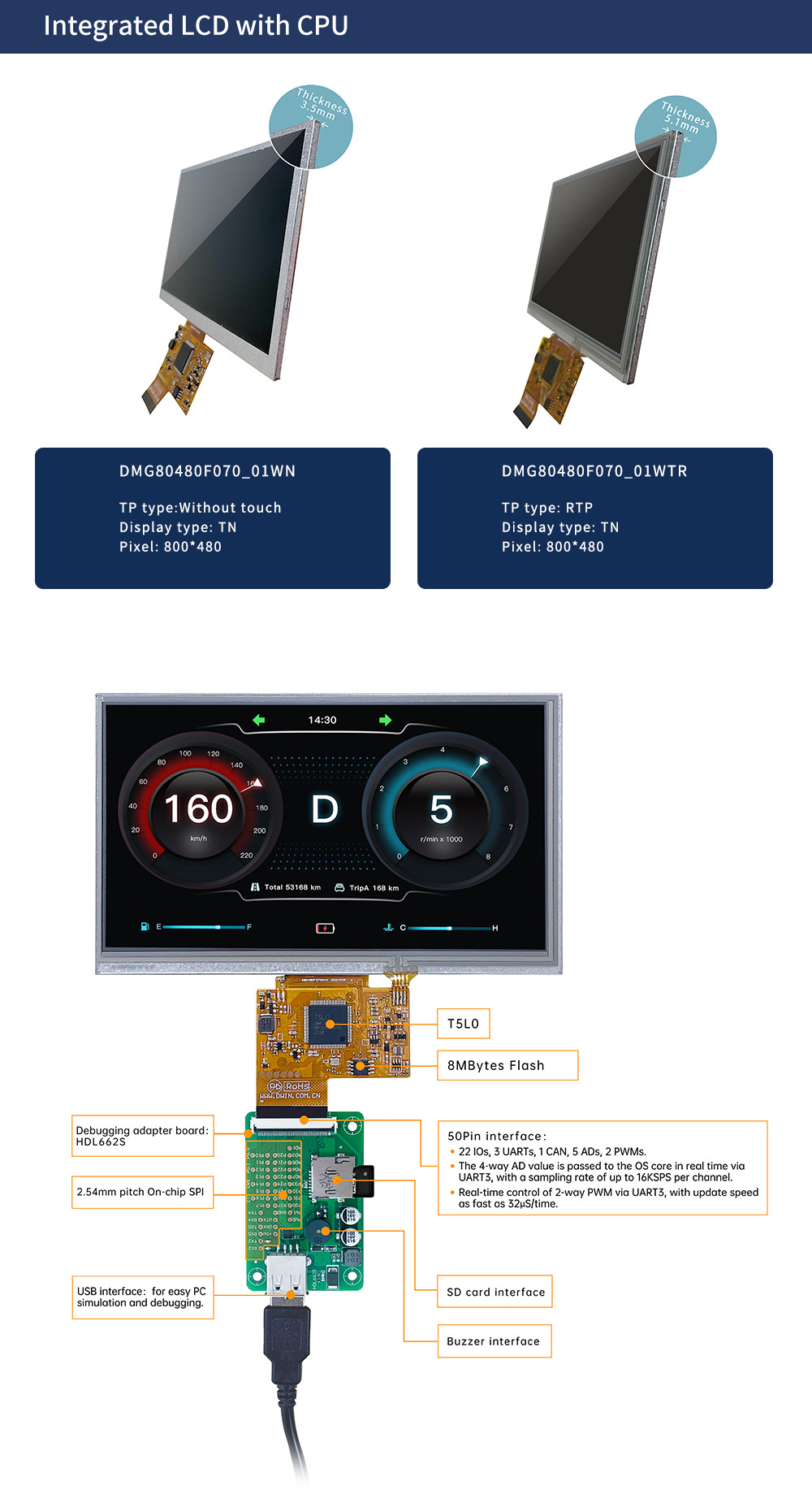

| T5L0 ASIC | DWIN द्वारे विकसित.2020 मध्ये मोठ्या प्रमाणावर उत्पादन, 1MBytes किंवा चिपवर फ्लॅश, OS CPU कोअर आणि मेमरीसह डेटाची देवाणघेवाण करण्यासाठी 128Kbytes व्हेरिएबल स्टोरेज स्पेस.पुनर्लेखन चक्र: 100,000 पेक्षा जास्त वेळा | ||

| रंग | 262K रंग | ||

| एलसीडी प्रकार | TN, TFT LCD | ||

| पाहण्याचा कोन | सामान्य पाहण्याचा कोन, 70°/70°/30°/40°(L/R/U/D) चे सामान्य मूल्य | ||

| डिस्प्ले एरिया (AA) | १५४.०८ मिमी (डब्ल्यू)×८५.९२ मिमी (एच) | ||

| ठराव | 800×480 | ||

| बॅकलाइट | एलईडी | ||

| चमक | DMG80480F070_01WN: 250nit | ||

| DMG80480F070_01WTR: 200nit | |||

| प्रकार | RTP (प्रतिरोधक स्पर्श पॅनेल) | ||

| रचना | ITO फिल्म + ITO ग्लास | ||

| टच मोड | समर्थन बिंदू स्पर्श आणि ड्रॅग | ||

| पृष्ठभागाची कडकपणा | 3H | ||

| प्रकाश संप्रेषण | ८०% पेक्षा जास्त | ||

| जीवन | डॉटिंग > 1,000,000 वेळा;स्ट्रोक > 100,000 वेळा;150 ग्रॅम बल, परत आणि पुढे दोनदा मोजले | ||

| पॉवर व्होल्टेज | 3.6~5.5V | ||

| ऑपरेशन चालू | VCC = +5V, बॅकलाइट चालू, 410mA | ||

| VCC = +5V, बॅकलाइट बंद, 115mA | |||

| कार्यरत तापमान | -10℃~60℃ | ||

| स्टोरेज तापमान | -20℃~70℃ | ||

| कार्यरत आर्द्रता | 10%~90%RH, 60% RH चे ठराविक मूल्य | ||

| बॉडरेट | 3150~3225600bps | ||

| आउटपुट व्होल्टेज | आउटपुट 1, Iout = 8mA;3.0~3.3V | ||

| आउटपुट 0, Iout =-8mA;0~0.3V | |||

| इनपुट व्होल्टेज(RXD) | इनपुट 1;3.3V | ||

| इनपुट 0;0~0.5V | |||

| इंटरफेस | UART2: TTL; | ||

| UART4: TTL; (ओएस कॉन्फिगरेशननंतरच उपलब्ध) | |||

| UART5: TTL; (ओएस कॉन्फिगरेशननंतरच उपलब्ध | |||

| डेटा स्वरूप | UART2: N81; | ||

| UART4: N81/E81/O81/N82;4 मोड (OS कॉन्फिगरेशन) | |||

| UART5: N81/E81/O81/N82;4 मोड (OS कॉन्फिगरेशन) | |||

| सॉकेट | 50Pin_0.5mm FPC | ||

| फ्लॅश | 8M बाइट्स | ||

| पिन | व्याख्या | I/O | कार्यात्मक वर्णन |

| 1 | +5V | I | वीज पुरवठा, DC3.6-5.5V |

| 2 | +5V | I | |

| 3 | GND | GND | GND |

| 4 | GND | GND | |

| 5 | GND | GND | |

| 6 | AD7 | I | 5 इनपुट ADCs.3.3V वीज पुरवठ्याच्या बाबतीत 12-बिट रिझोल्यूशन.0-3.3V इनपुट विद्युतदाब.AD6 वगळता, उर्वरित डेटा UART3 in द्वारे OS कोरला पाठविला जातो 16KHz सॅम्पलिंग रेटसह रिअल टाइम.AD1 आणि AD5 मध्ये वापरले जाऊ शकते समांतर, आणि AD3 आणि AD7 समांतर वापरले जाऊ शकतात, जे दोन समान आहेत 32KHz सॅम्पलिंग AD.AD1, AD3, AD5, AD7 समांतर वापरले जाऊ शकते, जे 64KHz सॅम्पलिंग AD च्या बरोबरीचे;डेटा 1024 वेळा बेरीज केला आहे आणि नंतर ओव्हरसॅम्पलिंग करून 64Hz 16bit AD मूल्य प्राप्त करण्यासाठी 64 ने भागले. |

| 7 | AD6 | I | |

| 8 | AD5 | I | |

| 9 | AD3 | I | |

| 10 | AD1 | I | |

| 11 | +३.३ | O | 3.3V आउटपुट, 150mA चे कमाल लोड. |

| 12 | SPK | O | बजर किंवा स्पीकर चालविण्यासाठी बाह्य MOSFET.बाह्य 10K रेझिस्टर पॉवर-ऑन कमी पातळी आहे याची खात्री करण्यासाठी जमिनीवर खाली खेचले पाहिजे. |

| 13 | SD_CD | IO | SD/SDHC इंटरफेस, SD_CK 22pF कॅपेसिटर जवळ GND ला जोडतो SD कार्ड इंटरफेस. |

| 14 | SD_CK | O | |

| 15 | SD_D3 | IO | |

| 16 | SD_D2 | IO | |

| 17 | SD_D1 | IO | |

| 18 | SD_D0 | IO | |

| 19 | PWM0 | O | 2 16-बिट PWM आउटपुट.बाह्य 10K रेझिस्टर खाली खेचले पाहिजे पॉवर-ऑन कमी पातळी आहे याची खात्री करण्यासाठी जमीन.OS कोर रिअल टाइममध्ये UART3 द्वारे नियंत्रित केला जाऊ शकतो |

| 20 | PWM1 | O | |

| 21 | P3.3 | IO | दोन्ही IO शी कनेक्ट करण्यासाठी RX8130 किंवा SD2058 I2C RTC वापरत असल्यास, SCL P3.2 शी कनेक्ट केले पाहिजे आणि SDA P3.3 शी समांतर कनेक्ट केले पाहिजे. 3.3V पर्यंत 10K रेझिस्टर पुल-अप सह. |

| 22 | P3.2 | IO | |

| 23 | P3.1/EX1 | IO | हे एकाच वेळी बाह्य व्यत्यय 1 इनपुट म्हणून वापरले जाऊ शकते, आणि कमी व्होल्टेज पातळी किंवा ट्रेलिंग एज इंटरप्ट मोड या दोन्हींना सपोर्ट करते. |

| 24 | P3.0/EX0 | IO | हे एकाच वेळी बाह्य व्यत्यय 0 इनपुट म्हणून वापरले जाऊ शकते, आणि कमी व्होल्टेज पातळी किंवा ट्रेलिंग एज इंटरप्ट मोड या दोन्हींना सपोर्ट करते. |

| 25 | P2.7 | IO | IO इंटरफेस |

| 26 | P2.6 | IO | IO इंटरफेस |

| 27 | P2.5 | IO | IO इंटरफेस |

| 28 | P2.4 | IO | IO इंटरफेस |

| 29 | P2.3 | IO | IO इंटरफेस |

| 30 | P2.2 | IO | IO इंटरफेस |

| 31 | P2.1 | IO | IO इंटरफेस |

| 32 | P2.0 | IO | IO इंटरफेस |

| 33 | P1.7 | IO | IO इंटरफेस |

| 34 | P1.6 | IO | IO इंटरफेस |

| 35 | P1.5 | IO | IO इंटरफेस |

| 36 | P1.4 | IO | IO इंटरफेस |

| 37 | P1.3 | IO | IO इंटरफेस |

| 38 | P1.2 | IO | IO इंटरफेस |

| 39 | P1.1 | IO | IO इंटरफेस |

| 40 | P1.0 | IO | IO इंटरफेस |

| 41 | UART4_TXD | O | UART4 |

| 42 | UART4_RXD | I | |

| 43 | UART5_TXD | O | UART5 |

| 44 | UART5_RXD | I | |

| 45 | P0.0 | IO | IO इंटरफेस |

| 46 | P0.1 | IO | IO इंटरफेस |

| 47 | CAN_TX | O | CAN इंटरफेस |

| 48 | CAN_RX | I | |

| 49 | UART2_TXD | O | UART2 (OS कोरचा UART2 सिरीयल पोर्ट) |

| 50 | UART2_RXD | I |